# Dense Instruction Set Computer Architecture

submitted by

Olaf S. Schoepke

for the degree of Ph.D

of the

University of Bath

1992

Attention is drawn to the fact that copyright of this thesis rests with its author. This copy of the thesis has been supplied on the condition that anyone who consults it is understood to recognise that its copyright rests with its author and that no quotation from the thesis and no information derived from it may be published without the prior written consent of the author.

This thesis may be made available for consultation within the University Library and may be photocopied or lent to other libraries for the purposes of consultation.

Olaf S. Schoepke

UMI Number: U601603

#### All rights reserved

#### INFORMATION TO ALL USERS

The quality of this reproduction is dependent upon the quality of the copy submitted.

In the unlikely event that the author did not send a complete manuscript and there are missing pages, these will be noted. Also, if material had to be removed, a note will indicate the deletion.

#### UMI U601603

Published by ProQuest LLC 2013. Copyright in the Dissertation held by the Author.

Microform Edition © ProQuest LLC.

All rights reserved. This work is protected against

All rights reserved. This work is protected against unauthorized copying under Title 17, United States Code.

ProQuest LLC 789 East Eisenhower Parkway P.O. Box 1346 Ann Arbor, MI 48106-1346

## Summary

Processor speed is still increasing. Memory cycle time cannot keep up with this development and is proving to be the limiting factor in high performance architectures. The gap between processor and memory speed must be bridged if future processors are to reach their full potential. In this dissertation an attempt has been made to solve the problem by increasing instruction density. A new computer architecture based on dense computer instruction sets is presented. Experimental results show that most of the compiled code can be generated using a small number of opcodes. Entropy measurements reveal very low entropy in instruction streams especially when treated as higher order Markov sources. Arithmetic coding, a coding technique capable of encoding close to the entropy bound, is used to encode and decode the instruction stream. A high level VLSI design is suggested for the architecture. Simulation results show a significant reduction in memory-processor bandwidth using a context dependent model for instruction set encoding.

# Acknowledgment

Thanks are expressed to my supervisor, Jeremy Bennett, for support and advice during this research work.

My appreciation also extends to other members of the *University of Bath*: Geoff Smith for proof-reading and many helpful discussions, Robert Oddy and Francesco Arci for proof-reading, and Chris Burdorf for valuable help with my publications.

I am also grateful to my parents for their constant support during this period.

A special thank you to Elisabeth without whose moral support and encouragement I would probably never have experienced university life.

Financial support for this research work from Siemens is kindly acknowledged.

## **Preface**

Each new generation of processing technology produces faster, dynamic RAMs with larger capacity than before. Nevertheless, the main memory cycle time has been decreasing less rapidly than the clock period for processors [Hennessy & Patterson 1990]. Although today's computer designer can choose from a wide variety of communication organizations, interaction between memory and processor remains a focal point in the design of high performance systems. As processors get faster more and more performance is lost to the memory system. A new memory-processor organization has to be evolved to supply instructions to the execution unit fast enough, and thus reduce communication delays.

In this dissertation I present a computer architecture based on dense computer instruction sets [Schoepke 1992d, Schoepke 1992g] to overcome the problem of increasing memory latency by the drastic reduction of memory-processor bus traffic through compact encoding. Dense computer instruction sets are the most promising way to reduce memory-processor bus traffic considerably, and thus reduce memory latency, to improve overall system performance. In developing this methodology an advanced architecture has been designed and its implementation simulated.

# Contents

| 1 | Intr | oducti | ion                               | 1  |

|---|------|--------|-----------------------------------|----|

|   | 1.1  | Archit | tectures                          | 1  |

|   | 1.2  | Progra | am Size                           | 3  |

|   | 1.3  | Memo   | ory Latency                       | 4  |

|   | 1.4  | Memo   | ory-Processor Connection          | 4  |

|   | 1.5  | Netwo  | orking                            | 5  |

|   | 1.6  | Inform | nation Theory                     | 6  |

|   | 1.7  | Summ   | ary                               | 6  |

| 2 | Bac  | kgroui | nd Theory                         | 7  |

|   | 2.1  | Analys | sis of High Level Language Usage  | 7  |

|   | 2.2  | Analys | sis of Instruction Sets           | 10 |

|   | 2.3  | Comp   | uter Architectures                | 12 |

|   |      | 2.3.1  | RISC Architecture                 | 13 |

|   |      | 2.3.2  | Shared Memory Architecture        | 14 |

|   |      | 2.3.3  | Improving Main Memory Performance | 17 |

|   |      | 2.3.4  | Cache Influence                   | 18 |

|   | 2.4  | Instru | ction Execution                   | 19 |

|   | 2.5  | Archit | ectural Solutions                 | 21 |

|   |      | 2.5.1  | Superscalar Designs               | 21 |

|   |      | 2.5.2  | Primitive Based Architectures     | 22 |

|   |      | 2.5.3  | Very Long Instruction Words       | 23 |

|   |     | 2.5.4 Micro-Architectural Parallelism                       | 23 |  |

|---|-----|-------------------------------------------------------------|----|--|

|   |     | 2.5.5 Distributed Instruction Set Computer Architecture     | 24 |  |

|   | 2.6 | 2.6 Theoretical Analysis of Instruction Sets                |    |  |

|   |     | 2.6.1 Overview                                              | 25 |  |

|   |     | 2.6.2 Replacement of Repeated Strings                       | 28 |  |

|   |     | 2.6.3 Memory Referencing Behaviour                          | 29 |  |

|   | 2.7 | Summary                                                     | 30 |  |

| 3 | ΑΊ  | Carget Architecture for Experimental Compression            | 31 |  |

|   | 3.1 | SPARC Architecture                                          | 31 |  |

|   | 3.2 | Instruction Description                                     | 33 |  |

|   | 3.3 | Performance                                                 | 37 |  |

|   | 3.4 | Summary                                                     | 38 |  |

| 4 | Con | npression Techniques                                        | 39 |  |

|   | 4.1 | Non Suitable Compression Techniques                         | 40 |  |

|   | 4.2 | Potentially Suitable Techniques                             | 40 |  |

|   |     | 4.2.1 Huffman Coding                                        | 40 |  |

|   |     | 4.2.2 A Universal Algorithm for Sequential Data Compression | 42 |  |

|   |     | 4.2.3 Prediction by Partial Matching                        | 42 |  |

|   |     | 4.2.4 Arithmetic Coding                                     | 43 |  |

| 5 | The | e Implementation of Arithmetic Coding                       | 45 |  |

|   | 5.1 | The Idea of Arithmetic Coding                               | 45 |  |

|   | 5.2 | Models for Arithmetic Coding                                | 46 |  |

|   | 5.3 | Simple Character Set Example                                | 47 |  |

|   | 5.4 | The Conventional Algorithm                                  | 49 |  |

|   | 5.5 | A Fast Decoding Algorithm for Arithmetic Coding             | 50 |  |

|   |     | 5.5.1 The Mathematics Behind Look-Up Tables                 | 51 |  |

|   |     | 5.5.2 Implementation                                        | 53 |  |

|   |     | 5.5.3 Experimental Results                                  | 54 |  |

|   |                                 | 5.5.4 Summary                                                                                                                                                                                                                                             | 55                                                 |

|---|---------------------------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----------------------------------------------------|

|   | 5.6                             | Hardware Implementation                                                                                                                                                                                                                                   | 56                                                 |

|   | 5.7                             | Summary                                                                                                                                                                                                                                                   | 56                                                 |

| 6 | Exp                             | perimental Results                                                                                                                                                                                                                                        | 57                                                 |

|   | 6.1                             | Experiments Performed                                                                                                                                                                                                                                     | 57                                                 |

|   | 6.2                             | Empirical Analysis                                                                                                                                                                                                                                        | 59                                                 |

|   |                                 | 6.2.1 Opcodes                                                                                                                                                                                                                                             | 59                                                 |

|   |                                 | 6.2.2 Opcode pairs                                                                                                                                                                                                                                        | 60                                                 |

|   |                                 | 6.2.3 Registers                                                                                                                                                                                                                                           | 60                                                 |

|   |                                 | 6.2.4 Constants                                                                                                                                                                                                                                           | 63                                                 |

|   |                                 | 6.2.5 Branch Instructions                                                                                                                                                                                                                                 | 64                                                 |

|   | 6.3                             | Entropy                                                                                                                                                                                                                                                   | 66                                                 |

|   | 6.4                             | Coding Results                                                                                                                                                                                                                                            | 70                                                 |

|   | 6.5                             | Summary                                                                                                                                                                                                                                                   | 72                                                 |

|   |                                 |                                                                                                                                                                                                                                                           |                                                    |

| 7 | Pro                             | posed Model for a Compressed Instruction Set Architecture based                                                                                                                                                                                           |                                                    |

| 7 |                                 | posed Model for a Compressed Instruction Set Architecture based                                                                                                                                                                                           | 74                                                 |

| 7 |                                 |                                                                                                                                                                                                                                                           | <b>74</b><br>74                                    |

| 7 | on S                            | SPARC                                                                                                                                                                                                                                                     |                                                    |

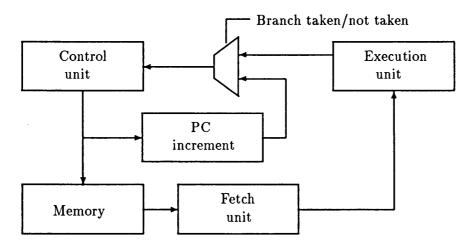

| 7 | on 9                            | SPARC Standard Execution Model                                                                                                                                                                                                                            | 74                                                 |

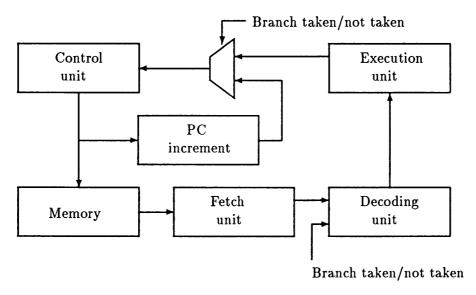

| 7 | on 5<br>7.1<br>7.2              | SPARC Standard Execution Model                                                                                                                                                                                                                            | 74<br>76                                           |

| 7 | on 5<br>7.1<br>7.2              | SPARC  Standard Execution Model                                                                                                                                                                                                                           | 74<br>76<br>77                                     |

| 7 | on 5<br>7.1<br>7.2              | SPARC  Standard Execution Model                                                                                                                                                                                                                           | 74<br>76<br>77<br>77                               |

| 7 | on 5<br>7.1<br>7.2              | SPARC  Standard Execution Model                                                                                                                                                                                                                           | 74<br>76<br>77<br>77<br>80                         |

| 7 | on 5<br>7.1<br>7.2              | SPARC  Standard Execution Model                                                                                                                                                                                                                           | 74<br>76<br>77<br>77<br>80<br>80                   |

| 7 | on 5<br>7.1<br>7.2<br>7.3       | Standard Execution Model                                                                                                                                                                                                                                  | 74<br>76<br>77<br>77<br>80<br>80<br>82             |

| 7 | on 5<br>7.1<br>7.2<br>7.3       | Standard Execution Model  Decode-Execution Model for Compressed Code  Handling Control Transfers  7.3.1 Overview of the Problem  7.3.2 Compiler Information  7.3.3 Solutions  7.3.4 Method Applied  Algorithms for Encoding and Decoding                  | 74<br>76<br>77<br>77<br>80<br>80<br>82<br>82       |

| 7 | 7.1<br>7.2<br>7.3<br>7.4<br>7.5 | Standard Execution Model  Decode-Execution Model for Compressed Code  Handling Control Transfers  7.3.1 Overview of the Problem  7.3.2 Compiler Information  7.3.3 Solutions  7.3.4 Method Applied  Algorithms for Encoding and Decoding  Cache Influence | 74<br>76<br>77<br>77<br>80<br>80<br>82<br>82<br>82 |

| Ω | Con | clusio | n                                              | 103 |

|---|-----|--------|------------------------------------------------|-----|

|   | 8.5 | Summ   | nary                                           | 102 |

|   | 8.4 | Archit | tecture Limits                                 | 101 |

|   |     | 8.3.5  | The Effect of Fetch Width                      | 100 |

|   |     | 8.3.4  | Effectiveness                                  | 99  |

|   |     | 8.3.3  | Comparison between Zero and First Order Model  | 98  |

|   |     | 8.3.2  | Compression Results compared to Theory         | 97  |

|   |     | 8.3.1  | Compression Achieved                           | 96  |

|   | 8.3 | Simula | ation Results                                  | 96  |

|   | 8.2 | A Sim  | ulator for Dense Instruction Set Architectures | 95  |

|   |     | 8.1.2  | Decoding                                       | 94  |

|   |     | 8.1.1  | Encoding                                       | 91  |

|   | 8.1 | Encod  | ling and Decoding Process                      | 91  |

# List of Figures

| 1-1 | Memory hierarchy                                                 | 3  |

|-----|------------------------------------------------------------------|----|

| 2-1 | Multiprocessor Bus Interconnection                               | 15 |

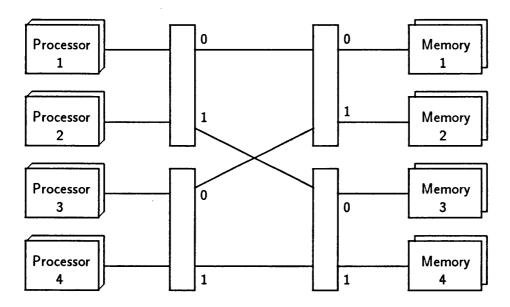

| 2-2 | Multiprocessor Crossbar Interconnection                          | 16 |

| 2-3 | Multistage Interconnection Network                               | 16 |

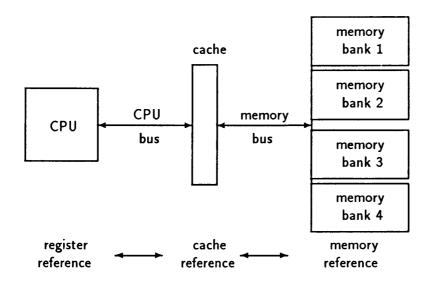

| 2-4 | Interleaved memory organization                                  | 17 |

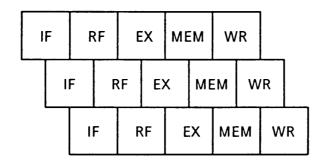

| 2-5 | Instruction pipeline                                             | 20 |

| 2-6 | Instruction super pipeline                                       | 21 |

| 2-7 | Superscalar structure                                            | 22 |

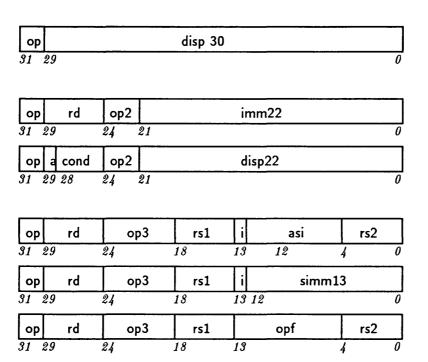

| 3-1 | Instruction formats                                              | 34 |

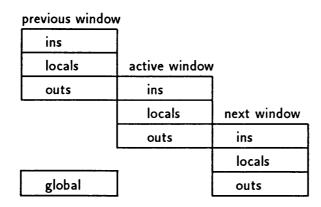

| 3-2 | SPARC register windows                                           | 36 |

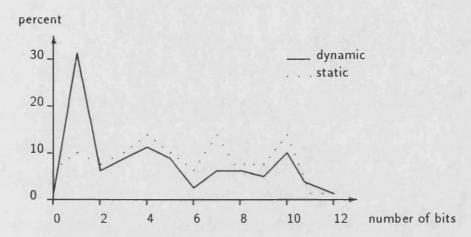

| 6-1 | Positive constant distribution                                   | 63 |

| 6-2 | Negative constant distribution                                   | 63 |

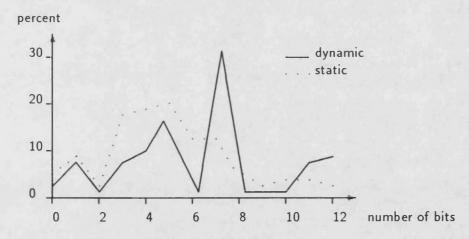

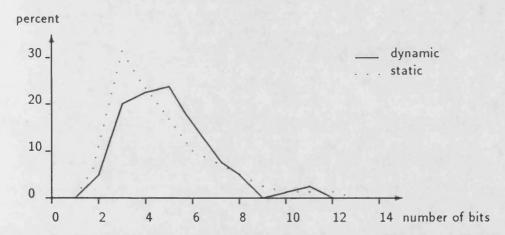

| 6-3 | Positive branch distribution                                     | 64 |

| 6-4 | Negative branch distribution                                     | 65 |

| 6-5 | Entropy for symbols and opcodes                                  | 67 |

| 6-6 | Register entropy for the dynamic case                            | 68 |

| 6-7 | Register entropy for the static case                             | 68 |

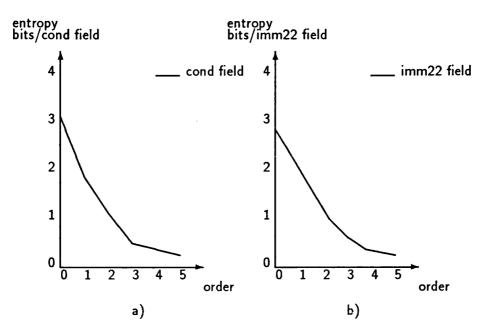

| 6-8 | Entropy for conditional and immediate field for the dynamic case | 69 |

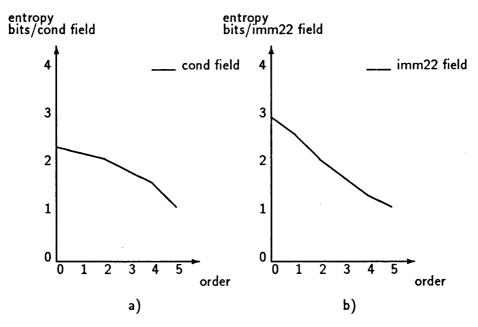

| 6-9 | Entropy for conditional and immediate field for the static case  | 69 |

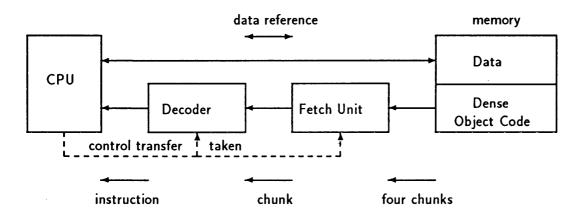

| 7_1 | Instruction execution                                            | 75 |

| <b>7-2</b> | Compressed object code execution                                | 76 |

|------------|-----------------------------------------------------------------|----|

| 7-3        | C code for if and for statement                                 | 78 |

| 7-4        | Assembler language for if and for statement                     | 78 |

| 7-5        | Encoding algorithm                                              | 83 |

| 7-6        | Decoding algorithm                                              | 84 |

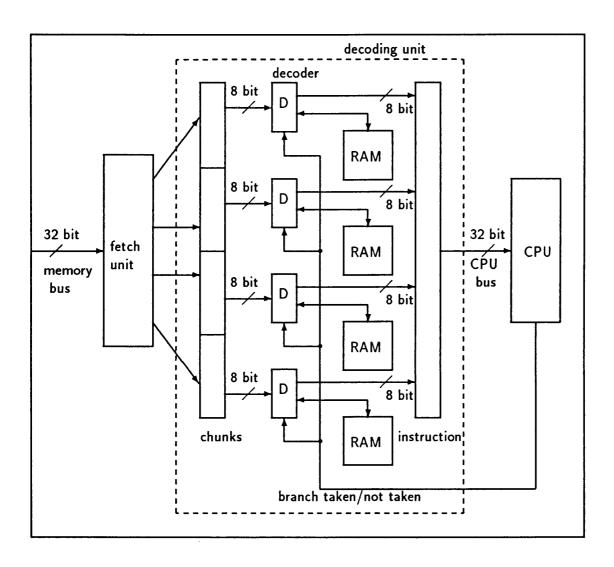

| 7-7        | VLSI Design for the dense instruction set computer architecture | 86 |

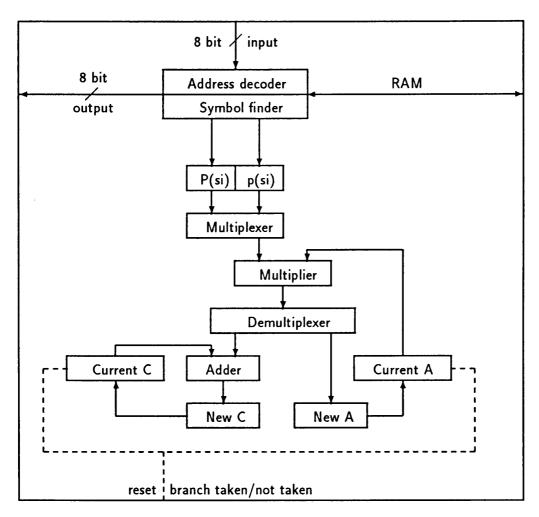

| 7-8        | Hardware design for arithmetic coding                           | 87 |

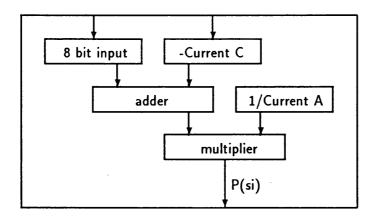

| 7-9        | Address decoder                                                 | 88 |

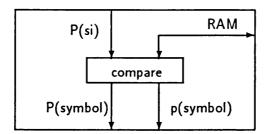

| 7-10       | Symbol finder                                                   | 89 |

| 0 1        | Encoding graph                                                  | വ  |

| 0-1        | Encoding graph                                                  | 92 |

| 8-2        | Simulator                                                       | 95 |

# List of Tables

| 2.1  | High level language usage                                     | 8  |

|------|---------------------------------------------------------------|----|

| 2.2  | Speed changes for caches                                      | 18 |

| 2.3  | Entropy obtained by Bennett                                   | 27 |

| 2.4  | $	ilde{H}$ obtained by Hammerstrom and Davidson               | 30 |

| 3.1  | Instruction description                                       | 35 |

| 5.1  | Simplified character set for arithmetic coding                | 47 |

| 5.2  | Calgary compression corpus                                    | 50 |

| 5.3  | Average number of search loop executions during decoding      | 51 |

| 5.4  | Miss distribution for the improved decoding algorithm         | 54 |

| 5.5  | Improved decoding results                                     | 55 |

| 6.1  | Opcode distribution                                           | 59 |

| 6.2  | Distribution of opcode pairs                                  | 60 |

| 6.3  | Register distribution for the static case                     | 61 |

| 6.4  | Register distribution for the dynamic case                    | 61 |

| 6.5  | Register distribution                                         | 62 |

| 6.6  | Branch distribution                                           | 66 |

| 6.7  | Program description                                           | 70 |

| 6.8  | Encoded object code results for a fixed model in static case  | 71 |

| 6.9  | Encoded object code results for a fixed model in dynamic case | 71 |

| 6.10 | Compression schemes                                           | 72 |

| 6.11 | Encoding results published by Bell et.al                      | 72 |

| 7.1 | Static and dynamic branch frequency                               | <b>7</b> 9 |

|-----|-------------------------------------------------------------------|------------|

| 8.1 | Compression results using a zero order model                      | 97         |

| 8.2 | Compression results using a first order model                     | 97         |

| 8.3 | Compression results compared to entropy using a zero order model  | 98         |

| 8.4 | Compression results compared to entropy using a first order model | 98         |

| 8.5 | Entropy improvement from zero to first order model                | 99         |

| 8.6 | Comparison between zero and first order model                     | 99         |

| 8.7 | Effectiveness                                                     | 100        |

| 8.8 | Wasted bits using a zero order model                              | 100        |

| 8.9 | Wasted bits using a first order model                             | 101        |

# Glossary

AMAT Average Memory Access Time

BN Branch Never

CISC Complex Instruction Set Computer

CPI Cycles per Instruction

CPU Central Processing Unit

DISC Distributed Instruction Set Computer Architecture

DMC Dynamic Markov Compression

DRAM Dynamic Random Access Memory

EX Execution

HLL High Level Language

IF Instruction Fetch

LZ Lempel and Ziv compression algorithm [Ziv & Lempel 1978]

LZB LZ Bell [Bell 1987]

LZFG LZ Fiala and Greene [Fiala & Greene 1989]

LZW Lempel Ziv Welch [Welch 1984]

MEM Data Memory Access

MIN Multistage Interconnection Network

PC Program Counter

PPM Prediction by Partial Matching

PPMC PPM using method C [Moffat 1990]

RAM Random Access Memory

RF Register Fetch

RISC Reduced Instruction Set Computer

SPARC Scalable Processor Architecture

VLIW Very Long Instruction Word

VLSI Very Large Scale Integration

WR Write Register Result

## Chapter 1

## Introduction

The main thrust in computer architecture design in the seventies was to reduce the semantic gap between high-level languages and machine language. Complex instructions were designed to denote a more substantial component of the user's intended application. One consequence was that a program composed of complex instructions performed the same task as before, but required less memory traffic during execution. In theory such instruction set also allowed the execution unit to run at peak performance more often. An important goal in high-performance architectures is to keep traffic density low on long and shared interconnections [Stone 1990].

#### 1.1 Architectures

In the eighties RISC (Reduced Instruction Set Computer) technology [Fox et al. 1986, Hopkins 1987, Katevenis 1984, Patterson & Séquin 1982] has emerged to simplify computer architecture. Instructions are few and simple and control can often be implemented in hardware, removing the overhead of microcode. Design complexity is reduced.

One problem is that static object code size and dynamic object code size 1 could be

<sup>&</sup>lt;sup>1</sup>Static code size is used to mean the code generated by the compiler, prior to execution, and describes the amount of memory occupied by the compiled program. Dynamic code size is used to mean the code executed during program run time. Thus, for example, a loop can occupy very little static code size, but huge dynamic code size (depending on the number of loop executions).

significantly larger than for CISCs (Complex Instruction Set Computers). As a result, more memory is required. This applies to caches, main memory, and secondary memory. In addition, memory-processor bus traffic is increased. Much of the work, in particular the design of an advanced architecture, will aim to minimize dynamic code size, since this will increase execution speed.

The problem of increased traffic is multiplied in shared memory multiprocessors where several processes require access to one memory bus. To accommodate several high-performance processors on a single memory bus, the architecture must reduce the bus demands of each processor.

Today the trend is towards an architecture with the best of both worlds. Multicycle instructions can be incorporated successfully into RISC architecture if they improve overall performance without compromising the basic cycle time. This dissertation attempts to increase the benefit of both design methodologies, more object code compactness and less bus loading than CISC, but more speed than RISC.

The increased traffic, both on- and off-chip, requires drastic changes in computer architecture, more so because of the increasing gap between memory and processor cycle time [Hennessy & Jouppi 1991, Hennessy & Patterson 1990, Klaiber & Levy 1991, Kurian et al. 1991].

There are several techniques used to hide memory latency, such as caches both onand off-chip which certainly reduce the amount of data transferred between memory

and processor. But no technique known to the author actually decreases memoryprocessor bus traffic down to the bounds possible [Hammerstrom & Davidson 1977,

Schoepke 1992c] according to information theory. Experiments carried out show very

low entropy for higher order Markov sources [Abramson 1963] in static as well as dynamic object code [Bennett 1988, Schoepke 1992c]. Such low entropy requires a compression technique which can encode into less than one bit per character.

While a number of research projects are focused on building scalable multiprocessors (scalable to hundreds or thousands of processors) using microprocessor technology, most of the focus in industry is on building small, bus-based machines that support cache coherency [Hennessy & Jouppi 1991]. To accommodate several high-performance

processors on a memory bus, the architecture must reduce the bus demands of each processor. However, as machine organizations gradually succeed in sustaining multiple instructions execution concurrently in each processor, they will demand greater bandwidth from local memory.

The work performed by Wade and Stigall [Wade & Stigall 1975], Hammerstrom and Davidson [Hammerstrom & Davidson 1977], and Bennett [Bennett 1988] already show what can be achieved in instruction design.

### 1.2 Program Size

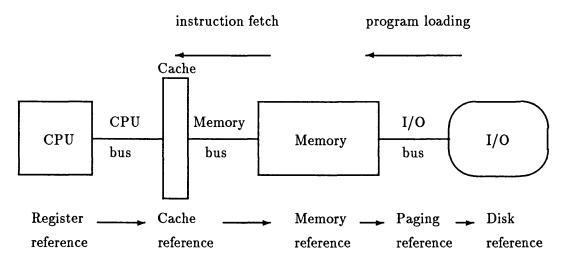

Programs get larger and larger and the demand for large memory continues to increase [Hennessy & Patterson 1990]. The tendency to use larger memory systems reduces speed as well. The program used requires memory on disk before loading, needs space on the bus during loading and main memory during run time, thus wasting space with redundant information. Figure 1-1 gives us an example of a typical memory hier-

Figure 1-1: Typical memory hierarchy with instruction and reference paths.

archy and the instruction path as well as the memory reference path.

Measurements by Bennett [Bennett 1988] have shown that most of the time people sit in huge programming environments, using commands with small execution times.

Therefore loading times are much more important than is usually appreciated. The memory used by the object code is also in competition with the data memory needed by the average program.

### 1.3 Memory Latency

Main memory satisfies the demands for caches and vector units as well as serving as the I/O interface. Unlike caches, performance measures of main memory emphasize both latency and bandwidth whereas main memory latency (which affects the cache miss penalty [Hennessy & Patterson 1990]) is the primary concern for caches. A 16MHz PC for example with only one wait state in its memory is slower than another PC that runs at 12MHz with no wait state. Even if the wait state penalty may be only one cycle, it occurs for every memory reference. Techniques that can cope with the large latency of memory accesses [Gupta et al. 1991] are essential for achieving high processor throughput. Coherent caches allow shared read-write data to be cached and significantly reduce the memory latency seen by the processor.

Prefetching techniques hide latency by bringing data close to the processor before it is actually needed. These techniques provide performance improvement, but were found to be very application dependent [Gupta et al. 1991]. Furthermore, prefetching instructions increases the number of instructions transferred between memory and processor and can end up in prefetching instructions that will never be executed.

### 1.4 Memory-Processor Connection

Researchers already talk about processors with 1000MIPS and their associated problems. Available bandwidth and latency, not computational speed, will be the main constraint to increase processor performance in the future.

For the 80386 or RISC architectures like SPARC, RISC I or RISC II, where only a single memory port is used for instructions and data access, compact code is even more important. One memory port means that only one access may be in process at any time. The SPARC and 80386 processor for example are both based on the load

and store von Neumann architecture. Hence, both can be significantly limited by the memory bandwidth. Assuming a cache hit on SPARC no penalty is incurred. For a cache miss, however, the processor stalls twelve cycles while the line is loaded into the cache. Many cycles are potentially wasted for data transfer operations between the main memory and the CPU internal registers. The data traffic is also competing against the instruction flow from main memory to the CPU, because only a single memory port is provided. Recent work by Ousterhout [Ousterhout 1990] shows that programs run slower on fast machines than the raw speed up would indicate. He believes that low memory bandwidth is one of the reasons for these results.

Introducing caches improve performance significantly, but cache misses are costly. Consider the Fairchild Clipper which has a four kbyte instruction and a four kbyte data cache. The average cache access time is 90nsec, the average memory access time is 400nsec. Assuming a hit rate of 90% the average access time would be 130nsec<sup>2</sup>. This is an increase of nearly 45% in access time compared with a 100% cache hit rate.

Branch prediction strategies are used to improve system performance after a branch has occurred through prefetching instructions at the address concerned. One problem with branch prediction strategies is that unnecessary memory accesses for instructions can be made which will never be executed. This can drastically reduce the amount of memory bandwidth available to the processor. An investigation into this problem has been published by Kaeli and Emma [Kaeli & Emma 1991]. They concluded that branch history tables are an effective approach to reduce latencies that arise looking at taken branches.

## 1.5 Networking

In networked systems the problem of large object code gets even worse, and swapping and paging across the network seems to be the biggest memory problem for diskless stations. Networks, built with server and several diskless stations, are most common

<sup>&</sup>lt;sup>2</sup>The formula for the average cycle time  $t_{eff}$  is  $t_{eff} = t_{cache} + (1-h)t_{main}$  where h is the probability of a cache hit and the time  $t_{cache}$  and  $t_{main}$  are the respective cycle times of cache and main memory. The quantity (1-h) is the probability of a cache miss.

these days. Serving several Mbyte of code to many diskless stations is not an easy task: disk I/O and transfer through the network account for most of the time spent for executing a short command of up to ten seconds execution time [Bennett 1988]. Loading times, especially across the network, are a far bigger problem than often expected. Object code is a major factor for bus traffic.

### 1.6 Information Theory

According to information theory, object code compression by more than factor ten is possible considering a fifth order model using eight bit long symbols on SPARC [Schoepke 1992c]. The amount of memory used to store information needed for encoding and decoding is related directly to the order of the model used. Using models of order ten brings the entropy down to 0.06 bit per symbol, but the amount of memory necessary to store the context information is tremendous.

### 1.7 Summary

For RISCs, the amount of memory which is occupied by object code has increased. Furthermore, dynamic code size increases and therefore memory-processor bus traffic increases. Drastic changes in the architecture are required to deal with this demand. The solution I am looking for is a compromise of the compression ratio achievable with high order Markov sources (such as order ten) and the amount of memory acceptable to store the necessary information.

## Chapter 2

## **Background Theory**

In this chapter background information is provided on usage of high level languages (HLLs), instruction sets, strategies for architecture improvements, and information theory. <sup>1</sup> "In any design work it is important to get a feel for the overall structure of languages." [Bennett 1988]

## 2.1 Analysis of High Level Language Usage

Analysis of HLL usage is essential to get information about instruction usage and the related problems. Several researchers examined language and instruction usage on different machines for various programming languages to find the best representation of a HLL program for execution. From the code size point of view, static measurements of programs are interesting. From the performance point of view, dynamic measurements of programs are generally more interesting than static measurements, but they are also more difficult to collect. Consequently there are fewer of them.

Weiker published a summary of sixteen analyses of high-level language usage gathered by several researchers [Weiker 1984]. He made an attempt to construct a synthetic benchmark program "Dhrystone" based on these recent statistics, particularly in the area of systems programming.

<sup>&</sup>lt;sup>1</sup>The term instruction set refers to the interface presented to the compiler writer by the architecture. The term architecture means the complete hardware of the computer, supporting the instruction set.

Weiker gave a brief characterization of all sixteen different data collections and several tables, which summarized the static statistics as well as dynamic statistics. Table 2.1 shows the variety of collected data for several HLL constructs for static as well as dynamic case. In all cases the three constructs of assignments, procedure calls, and conditional branches dominated.

Language Usage

| <del></del> | assignments  | calls      | if          | other         |

|-------------|--------------|------------|-------------|---------------|

| static      | 33.7-54.0%   | 12.0-40.3% | 8.8 - 21.1% | 7.9%-31.9%    |

| dynamic     | 41.9 - 67.0% | 4.0-32.8%  | 7.7-36.0%   | 1.2%- $21.8%$ |

Table 2.1: High level language usage published by Weiker. Information is given about the distribution of different language statements.

In several other tables Weiker shows types of assignments, the distribution of the number of parameters in *calls*, number and type of operators and the locality of variables. The average number of parameters in *calls* varies from 0.9 [Cook & Lee 1982] to 2.1 [DePrycker 1982].

Weiker's work is an excellent summary – as has been shown by the great amount of interest in his Dhrystone Benchmark. Dhrystone is also used in this dissertation to measure the improvement achieved on reduced memory-processor bus traffic. It is worth looking in more detail at some of the work he summarizes and at more recent work.

Knuth was the first to publish work of analysis of the use of existing machines to provide data for future design for computer architecture [Knuth 1971]. He examined a range of FORTRAN programs from industry and academia. He discovered that the average expression has only two operands, indicating that support for complex expression evaluation is perhaps unjustified. In particular he noted that a large number of expressions were of the form x + 1 (40%) or  $y^2$  (39%).

About 4% of the statements were do loops of which most were quite short involving only one or two statements. Only 13% had more than five statements.

Knuth also distinguished between static and dynamic statistics, showing for the first time that optimization for program size and program speed require different concepts. When he examined twenty-four special programs, he showed how the relative frequency of statement types changes (although not greatly) when the counts are dynamic instead of static. Overall, Knuth's study showed that a small number of basic patterns account for most of the programming constructions in use and that programs generally are very simple.

Alexander and Wortman studied the static and dynamic characteristics of programs written in the language XPL [Alexander & Wortman 1975]. The nineteen XPL programs they examined included compilers written by undergraduate and graduate students as well as two principal components of the XPL system. For numeric constants they obtained the interesting result that 56% of all numeric constants could be represented using four bits, and 98% could be represented using 12 bits or less. Many of the numeric constants greater than  $2^{10}$  were, in fact, masks.

Tanenbaum made an empirical study of more than 10,000 lines of program text to propose an advanced machine architecture specifically designed for structured programs [Tanenbaum 1978]. The programs examined for his research were all written by the faculty and graduate students of a computer science group. Although this work was done much later and concerned a different language, in general they got the same result as Knuth during his FORTRAN study, i.e. programs tend to be very simple.

Patterson and Séquin looked at the frequency of classes of variables in high-level language programs (written in the programming languages C and Pascal) during their RISC project [Patterson & Séquin 1982]. Their most important observation was that integer constants appeared almost as frequently as arrays or structures. More than 80% of the scalars were local variables and more than 90% of the arrays or structures were global variables.

Bennett describes static frequencies of various BCPL statements [Bennett 1988]. In line with other researchers' results his figures are dominated by assignment, procedure call and conditionals, which together account for 82.7% of all statements.

#### Summary

Different analyses of language usage show that programs of a wide variety of types are generally very simple. During procedure calls only a few parameters are passed

and immediates and branch displacements use only a few bits to represent their value. These analyses suggest a great deal of redundancy in computer programs.

### 2.2 Analysis of Instruction Sets

Looking at high level constructs is not always a sufficient way of analysing language usage since the representation of statements with instructions differs widely. Assigning a constant to a simple variable is inevitably less verbose than assigning a result of a function call to a member of a structure. To get a feel of instruction set usage it is helpful to look at compiled code rather than a HLL.

Alexander and Wortman also studied instruction set usage during their XPL program analysis [Alexander & Wortman 1975]. They found a dominance of the *load* instruction: more than one out of four compiled or executed instruction is a *load*. Branch and condition and store instructions are both about as frequent, in the range 10-15%.

They also looked at instruction pairs and triples. They found that thirty out of forty-five distinct instructions emitted by the XPL compiler had fewer than four different instructions as possible successors. Therefore these instructions contain more information than just their own function, since they also constrain the possible instructions that might be executed next.

An analysis of branch instructions showed that 55% of the executed branches and 36% of the compiled branches were unconditional. It is interesting to note that over half the branches were no more than 128 bytes away from the location of the branch instruction. That means branch instruction carry a lot of redundant information in them.

Sweet and Sandman, using an analysis of the Mesa byte-stream instruction set, describe the refinement of the instruction set [Sweet & Sandman 1982]. They provide a formalization of the statistics required and the method to be used. Under their scheme to reduce the static size of compiled code, they propose a five stage design process:

#### 1. Normalize the object code:

Many of the instructions in existing object code were special versions of generic

instructions dealing with common cases. These were replaced by their generic instructions, to eliminate pre-supposition about what were "good" instructions. For example jump not zero was replaced by load zero followed by jump not equal.

#### 2. Collect statistics by pattern matching:

2.5 million bytes of code were analysed to find particular statistical information.

- Static opcode frequency: count the number of occurrences of each opcode;

- Operand values: for each opcode, get a histogram of operand values;

- Popular opcode pairs: for each opcode, get a histogram of the set of next opcodes in the code sequences; this includes opcode predecessors and opcode successors; these are the same items of information, but different representations are more useful at different times.

#### 3. Propose new instructions:

The statistics gathered were used to suggest new instructions through combining opcodes, opcode and argument, or arguments. The instruction pair LI 0, LI 0 (Load Immediate Zero) for example led to a new instruction LID0 (Load Immediate Double Zero).

#### 4. Peephole optimization:

Convert to new opcodes by peephole optimization.

5. Repeat steps 2 through 4 until you have enough instructions.

Normalization is an important concept in refining instruction sets. The existing instruction set utilized 240 out of a possible 256 instructions. Sweet and Sandman's normalized instruction set had 100 generic instructions, leaving scope for 156 new instructions.

For static frequencies Sweet and Sandman obtained the result that *load immediate* and *load local variable* were the most common instructions with 16.90% and 12.68% respectively. Over 6% of the instructions were procedure calls. In fact, only six instructions account for more than 50% of the opcodes. For *load immediate* instructions they found that 45.83% of arguments are zero and 14.01% are unity.

Cook describes a static analysis of the instructions used to implement the system software on the Lilith computer, including editors, document processors, window packages and other modules [Cook 1990]. The analyzed software was from 180 modules with 2236 procedures, comprised of 146293 instructions. All programming on Lilith was done in Modula-2.

Cook obtained the result that 20 out of 256 possible opcodes represent 50% of the usage of all instructions. Overall Cook got comparable results as Sweet and Sandman [Sweet & Sandman 1982] during their analysis about the Mesa instruction set.

During static analysis Bennett obtained similar results for BCPL programs namely that only a few instructions built most of the compiled code [Bennett 1988].

A recent analysis of MIPS and SPARC instruction set utilization using the SPEC benchmarks is given by Cmelik et.al. [Cmelik et al. 1991]. Although no details are given for single instruction or register usage, the results give a good overview on how instruction categories are used. In particular, their integer benchmark indicates that between 20.26% and 26.51% of all SPARC instructions measured are control transfer instructions (depending on the benchmark program used).

#### Summary

Different analyses of instruction set usage show that most of the compiled code is built with only a few instructions, far less than the number of instructions provided by the architecture. New instructions built from frequently used opcodes or opcode pairs can reduce program size. The analyses shown (undertaken by several researchers) demonstrate the simplicity of generated instruction streams.

## 2.3 Computer Architectures

Several techniques are known that can hide memory latency. Instruction sequencing, scheduling, and pipelining are only a few of them. Hiding memory latency is one of the main concerns of computer architects as the gap between memory and processor cycle times is still widening [Hennessy & Patterson 1990]. Caches can only alleviate this

problem as they have to be both, large and on-chip. Furthermore, the cache memory cycle time increases for larger cache size due to additional decode logic and loading of the bus (both internal and external to the memory chip) [Krick & Dollas 1991]. Certain memory organizations are able to reduce latency times, but not the amount of data transferred between memory and processor. Some can even increase traffic, such as prefetch techniques.

#### 2.3.1 RISC Architecture

Patterson and Séquin [Patterson & Séquin 1982] describe the Reduced Instruction Set Computer Project. The purpose of their project was to explore alternatives to the general trend towards architectural complexity. They expected a reduction in design time and design errors and much faster execution time for individual instructions. Patterson's and Séquin's project is one of the research projects that lead the way to the RISC architecture.

While there are many variations on the theme, most RISC processors have the following attributes in common [Colwell et al. 1985]:

#### Fewer instruction

Studies in the early days of RISC showed that most compilers used only 30% of the instruction sets provided by CISCs, such as DEC's VAX. RISC processors attempt to implement only that 30%, allowing the chip to be smaller, cheaper, and (in theory) faster.

#### Fewer instruction formats

RISCs generally have only a few instruction formats to maintain simplicity. Usually, all instructions are the same length such as in SPARC. Furthermore, on most processors instructions and data words are of the same size. For SPARC this means it can take more than one instruction to load a constant of more than 13 bits as the immediate operand is only 13 bits long. However, as most constants in computer programs are small numbers, a single add or or instruction suffices in most cases.

#### **Dummy register**

Most RISCs have a dummy register, a register with the hardwired value zero. Such a register is a convenient way to turn an instruction with two sources into an instruction with a single source without complicating the instruction set.

#### Load and store architecture

In most cases load and store instructions are the only instructions to access memory. All other instructions effect only the on-chip registers. This rule is violated on SPARC by allowing atomic load and store such as the swap instruction.

#### Limited addressing modes

Most RISCs have only simple addressing modes (indirect through a register), doing all address calculations in registers. However, implemented chips such as SPARC, allow also register-plus-displacement modes and some processors support a third addressing mode through forming a memory address by adding the contents of two internal registers.

#### Single cycle execution

Most RISC instructions are simple enough to require only one cycle. On some architectures multiple cycles are required by instructions such as *load* or *store*.

#### Delayed control transfers

To avoid wasted time, most RISCs allow an additional instruction to be inserted into the "delay slot" after the control transfer instruction before the branch is actually taken. Some processors such as SPARC can annul <sup>2</sup> this instruction.

#### 2.3.2 Shared Memory Architecture

Shared memory architecture accomplishes interprocessor coordination by providing a global, shared memory that each processor can address. Commercial shared memory

<sup>&</sup>lt;sup>2</sup>See section 3.1.

architectures were introduced during the 1980s. A typical first generation system was the Balance 8000 from Sequent Corporation, offered in 1984 with two to twelve National 32032 microprocessors. The 8000 was updated two years later by the 21000, offering up to 30 microprocessors. Two further commercial shared memory architectures are the Flex/32 from Flexible Corporation and the Multimax from Encore Computer. These architectures involved multiple general-purpose processors, sharing memory. Processes communicate through shared variables in memory. However, synchronization must be available to coordinate processes.

Shared memory computers avoid some of the problems encountered by message passing architectures, but the problems of data access synchronization and cache coherency must be solved. Typically, each processor in a shared memory architecture has also a local memory used as a cache. Multiple copies of the same shared memory data may therefore exist in various processors' caches at any given time. Maintaining a consistent version of such data is the cache *coherency* problem.

To maintain cache coherency a special protocol, called *snooping*, can be used. Each cache controller monitors, or *snoops*, on the bus to determine whether they have a shared block of data. This technique is popular on shared memory systems as it can use a pre-existing connection: the memory bus.

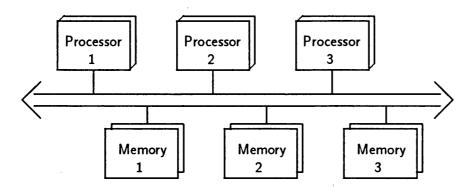

Figure 2-1: Multiprocessor Bus Interconnection

There are a number of ways of connecting multiple processors to shared memory [Duncan 1990]. Bus interconnection (Figure 2-1) offers the simplest way to give multiple processors access to shared memory. A single time-shared bus efficiently accommodates

a moderate number of processors, limited by the fact that only one processor may use the bus at any given time.

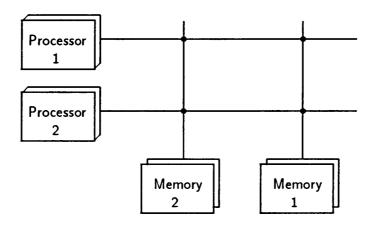

Figure 2-2: Multiprocessor Crossbar Interconnection

Crossbar interconnection (Figure 2-2) uses a crossbar switch of  $n^2$  crosspoints to connect n processors to n memories. Processors may contend for access to a memory location, but crossbars prevent contention for communication links by providing a dedicated pathway between each possible processor/memory pairing.

Figure 2-3: Multistage Interconnection Network

The multistage interconnection network (MIN) shown in Figure 2-3 strikes a compromise between the price/performance alternatives offered by crossbars and buses. An n \* n MIN connects n processors to n memories by deploying multiple stages or banks to switches in the interconnection network pathway. A processor making a memory access request specifies the desired destination and pathway by issuing a bit-value that contains a control bit for each stage. Multiprocessor performance heavely depends on the performance of the whole system when sharing data.

#### 2.3.3 Improving Main Memory Performance

Figure 2-4: Interleaved memory organization with four memory banks.

Main memory can be organized in banks (Figure 2-4) to give access to multiple words at a time rather than single words. The banks are one word wide so that cache as well as bus width need no changes. Organized in banks, main memory allows one clock cycle for each write (provided the writes are not destined to the same memory bank). This "mapping" of addresses to banks affects the memory behaviour as the memory address is interleaved.

The original motivation was to interleave sequencial memory accesses and to allow multiple independent accesses. This method, however, does not decrease the number of bytes to be transferred between main memory and processor. The memory bus is still the main bottleneck in the system.

#### 2.3.4 Cache Influence

One of the most important hardware techniques used to improve performance during the past decade has been caching; a technique which relies on using more hierarchical memory to achieve higher performance. Many researchers have investigated caches, their performance and improvements, and influence on different architectures, for example [Eickemeyer & Patel 1988, Farrens & Pleszkun 1989].

An instruction cache greatly speeds the instruction-sequencing requirements of the instruction fetch unit. A cache hit must occur to improve the apparent memory cycle time. To attain a peak execution rate of one instruction per cycle, the cache memory must have a cycle time less than or equal to the instruction fetch time. Memory access time, however, has to be "reasonable" so cache misses are not too costly. Second level caches between the primary cache and main memory can be used to reduce cache miss time.

| Speed Changes |          |           |            |  |  |  |

|---------------|----------|-----------|------------|--|--|--|

| Hit Rate      | Hit Time | Miss Time | Total Time |  |  |  |

| percent       | percent  | percent   | percent    |  |  |  |

| 100%          | 100%     | 0%        | 100%       |  |  |  |

| 99%           | 99%      | 26%       | 125%       |  |  |  |

| 98%           | 98%      | 52%       | 150%       |  |  |  |

| 95%           | 95%      | 130%      | 225%       |  |  |  |

Table 2.2: Speed changes as hit rate varies for the SPARCstation 2 with 26 cycle miss costs. The hit rate reduces from 100% to 95%. The effect on hit time, miss time and total time is shown.

Although the cache hit ratio is largely affected by cache size, increase in size must also be weighed against longer access time and higher costs. For a given memory technology, the cache memory cycle time increases for larger cache size due to additional decode logic and loading on the bus. Cache efficiency depends heavely on the cache hit rate. Table 2.2 provides information about speed changes for the SPARCstation 2 with a cache miss cost of 26 cycles [Cockcroft 1991] as the cache hit rate varies. Although a

hit rate of 95% sounds high, there is a dramatic increase in execution time compared with a 100% hit rate.

#### 2.4 Instruction Execution

Instruction sequencing is one of the fundamentals for von Neumann architectures, but it is complicated by interdependencies between instructions. High performance systems use a number of strategies to address these interdependencies in order to improve system performance. Krick and Dollas [Krick & Dollas 1991] discuss several aspects of instruction sequencing such as memory bandwidth, instruction buffers, and caches.

The memory address that contains the next instruction to be executed must be known before the instruction can be fetched and executed. A processor can achieve peak performance only when it does not have to wait for memory to provide the instruction required for execution. During the execution phase of each instruction, the processor determines the memory location of the next instruction to be executed. Instructions such as conditional branches can affect the address of the next instruction and the memory response could affect the availability of an instruction for execution. "Delayed jumps" as used in SPARC or R3000 offer the opportunity to insert an additional instruction in a branch slot which will be executed before the branch will be taken. Prefetching of instructions into a buffer and caches are two solutions which improve system performance [Hennessy & Jouppi 1991].

The past decade has seen renewed interest in instruction sequencing. Designers have proposed a variety of hardware and software approaches such as branch prediction strategies and instruction-scheduling techniques to further improve system performance.

Instruction scheduling or pipeline scheduling was first used in the 1960s and became an area of major interest in the 1980s, as pipelined machines became more widespread. The CDC 6600, delivered in 1964 by Control Data, was one of the first machines using an instruction scheduler [Thorlin 1967]. Rather than allowing a pipeline to stall, a compiler could try to avoid these stalls by rearranging the code sequence generated. Measurements undertaken with the DLX pipeline show that 54% of loads result in a

pipeline stall when using the gcc compiler. Using instruction scheduling the number decreases to 31% [Hennessy & Patterson 1990]. These pipelining *hazards* occur when, for example, the result of a load instruction is used by the next instruction as a source operand.

Instruction pipelining is a technique which allows the decomposition of instruction execution into a series of autonomous stages which can be executed independently. The first general-purpose pipelined machine is considered to be the IBM 7030. The more recently Mips R3000 architecture is implemented with a five stage pipeline. Figure 2-5 shows an example for a simple pipeline structure with three pipe stages.

| IF | RF | EX | MEM | WR  |     |    |

|----|----|----|-----|-----|-----|----|

|    | IF | RF | EX  | МЕМ | WR  |    |

| ·  |    | IF | RF  | EX  | мем | WR |

Figure 2-5: A simple machine pipeline with three pipe stages. (IF is used to mean instruction fetch, RF register fetch, EX execution, MEM data memory access, and WR write register result.)

In pipelining systems, subsequent instructions can be requested before the execution of the previous instruction has been completed. The problem is that conditional branch instructions, however, can alter the request of subsequent instructions in a pipelined system.

Pipelining improves the throughput of a machine by exploiting instruction-level parallelism without changing the basic cycle time. In fact, the execution time of each individual instruction can increase slightly due to overhead in the pipeline control. Instruction-level parallelism is available when instructions in a sequence are independent and can thus be executed in parallel by overlapping [Hennessy & Jouppi 1991]. The machine attains its performance benefits by increasing the number of pipeline stages in the processor and keeping all stages busy.

However deeply pipelined processors have relatively low issue rates <sup>3</sup> due to dependencies between instructions [Farrens & Pleszkun 1991]. Multiple instruction issue is offered by machines such as Apollo DN10000 and Intel i860.

Super pipelining increases performance even further. Using this technique, one step in the pipeline can be done in less than a machine cycle. Figure 2-6 shows an example for a simple pipeline structure with three pipe stages. The Mips R4000 architecture is implemented with a eight stage super pipeline using half the cycle time internally than externally. For R4000 super pipelining has been chosen against superscalar because it need less implementation logic on-chip [Gänsheimer & Reisch 1991].

Figure 2-6: A simple machine super pipeline with three pipe stages.

#### 2.5 Architectural Solutions

#### 2.5.1 Superscalar Designs

Superscalar designs are architectures that can execute more than one instruction per cycle. Hardware can be used to identify independent instructions which can be executed in parallel. Two major studies of scalar oriented programs have shown the practical level of exploitable parallelism to be around two operations per clock [Hennessy & Jouppi 1991]. All superscalar machines built to date restrict the combination of instructions that can be issued in one clock. One implementation is the IBM RS/6000 [Grohoski 1990]. Ini-

<sup>&</sup>lt;sup>3</sup>The process of letting an instruction move from the instruction decode stage into the execution stage of the pipeline is called instruction issue; the instruction that has made this step is said to have issued.

tial results from this work are very promising, and the commercial implementation and availability of these processors demonstrate a mature technology. The Intel 960 CA and Tandem Cyclone are two examples of superscalar machines with complex instruction sets. Figure 2-7 shows an example for a simple superscalar structure with two pipe stages.

| IF | RF | EX | МЕМ | WR  |    |

|----|----|----|-----|-----|----|

| IF | RF | EX | MEM | WR  |    |

|    | IF | RF | EX  | мем | WR |

|    | IF | RF | EX  | MEM | WR |

Figure 2-7: A simple superscalar structure with two pipe stages.

The limiting factor in increasing the instruction issue rate for a superscalar machine is probably the difficulty in fetching, decoding, and issuing an ever-larger number of instructions in the same clock cycle. One question yet to be resolved is whether the main memory organization of such processors can follow conventional designs, or whether the increased traffic requires drastic changes.

#### 2.5.2 Primitive Based Architectures

Fritsch et.al. [Fritsch et al. 1990] maintain that the only way to raise performance if code fetch bandwidth is limited, is to increase code density. For this purpose and to reduce the cycle time required by any conventional RISC architecture, they define a family of *Primitive Based Architectures*, characterized by uniformity of coding and fast parallel decoding. The difference between instructions and such *primitives* is that an instruction completely defines an operation, while a *primitive* of order n expresses the n elemental actions to be carried out, on arguments possibly defined by preceding actions.

For a primitive set for order two, for which they obtained the shortest code length, Fritsch et.al. evaluated primitive formats and a primitive set including conditional and unconditional branching, operations, memory access and other features like long literal handling and stack operations. Assuming the same register-window configuration as the Berkeley RISC-II [Katevenis 1984] and four stage pipeline in the processor, Fritsch et.al. achieved shorter code length and faster execution than the RISC-II machine during simulation.

#### 2.5.3 Very Long Instruction Words

Another approach to increase concurrency uses Very Long Instruction Words (VLIWs) [Fisher 1987]. Memory words contain more than one instruction, so each memory reference fetches multiple instructions. This architecture relies heavily on sophisticated compilers to generate the code required to use machine resources efficiently. A major impediment to such architectures is the conditional branch. When a conditional branch is pending, scheduling useful computations is difficult until the execution path becomes known.

In contrast to superscalar architectures, in VLIW architectures the compiler has complete responsibility for creating a package of instructions that can be issued simultaneously and the hardware does not makes the decisions about multiple issue. TRACE – built by Multiflow Computer – is a VLIW architecture [Colwell et al. 1987].

#### 2.5.4 Micro-Architectural Parallelism

Hwu and Chang [Hwu & Chang 1988] evaluated micro-architectural parallelism, including multiple instructions issued per cycle, multiple result distribution buses, multiple execution units and pipelined execution units. All of their architecture variations had a split register organization with 32 integer and 32 floating point registers. Code was generated with a prepass code generation strategy, which performed instruction scheduling before register allocation. Using the Livermore Loop and Linpack subroutines as benchmarks, Hwu and Chang concluded that, when used together, multiple instruction issue and pipelined execution units produced a speedup greater than the sum of speedups

of each taken separately. They also found that issuing more than two instructions per cycle produced little additional speedup.

Higher instruction execution rate also led to an increase in bus traffic as more instructions were fetched from memory per processor cycle.

#### 2.5.5 Distributed Instruction Set Computer Architecture

The Distributed Instruction Set Architecture (DISC) employs a new parallel instruction set and a distributed control mechanism to explore fine-grained parallel processing in a multiple-functional-unit system. Multiple instructions are executed in parallel and/or out of order at the highest speed of n instructions per cycle, where n is the number of functional units. Wang and Wu [Wang & Wu 1991] developed a hardware system and studied the performance level, the effect on program size and the hardware utilization. Their simulation results show that a DISC system incorporating 16 functional units can run 7.7 times faster than a single-functional-unit DISC system. DISC presents three major contributions in the domain of fine-grained multiprocessing:

- 1. Fast multiple instruction issuing mechanism: no decoding work is needed prior to issuing an instruction. Multiple instructions are fetched from memory and issued directly to multiple functional units.

- 2. Parallel and/or out-of-order execution: data dependency among functional units is maintained in a distributed manner. No hardware is required to coordinate multiple instruction executions. This minimizes the inter-unit communication and speeds up the overall execution rate.

- 3. Software dataflow: the post compiling idea is to tag each instruction with its data tag. This is equivalent to generating the data token in software and combining it with the instruction token. It pioneers a software dataflow control scheme for multiple-functional-unit systems.

In contrast to dense instruction sets, DISC is based on instruction independency. The results provided in Section 6.3 question these independencies. However, executing more than one instruction per cycle also implies that more instructions per cycle have

to be fetched from memory. Assuming an execution of two instructions per cycle, bus traffic at least doubles.

#### Summary

Bus demands increases not only for shared memory multiprocessors. In addition for processors which are able to execute more than one instruction per cycle the increasing bus traffic requires changes in the architecture to supply instructions to the execution unit fast enough.

# 2.6 Theoretical Analysis of Instruction Sets

The concepts of information theory and its mathematical analysis are established in Shannon's source coding theorem [Shannon 1948]. Many textbooks now provide an introduction to information theory, for example [Abramson 1963]. A number of attempts have been made to use information theory in instruction set design [Bennett 1988]. Modelling the structure of instruction sets has been used to estimate the most compact instruction set [Flynn & Hoevel 1984]. Entropy has been considered to examine static or dynamic code size [Bennett 1988, Wade & Stigall 1975] and redundancy in addressing [Hammerstrom & Davidson 1977].

Analysis involving the entropy of instruction streams offer far more hope. Entropy [Abramson 1963, Thomas 1991] is the key to compression and understanding entropy is vital to understanding compression.

#### 2.6.1 Overview

A zero-memory source is given by a sequence of symbols from an alphabet S

$$S = \{s_1, s_2, \dots, s_a\} \tag{2.1}$$

where the occurrence of a symbol is independent of previous symbols. Such an information source is described completely by the source alphabet S and the probabilities

with which the symbol occurs:

$$P(s_1), P(s_2), \ldots, P(s_a).$$

If symbol  $s_i$  occurs, one obtains an amount of information equal to

$$I(s_i) = -\log_2 P(s_i) \ bits \tag{2.2}$$

according to information theory [Shannon 1948]. The average amount of information obtained per symbol is thus

$$H(S) = \sum_{i=1}^{q} P(s_i)I(s_i) \ bits$$

where  $\sum_{i=1}^{q}$  means the summation over all q symbols. This quantity, H(S), the average amount of information per source symbol, is called the *entropy* of the zero-memory source. When a stream of symbols is encoded so it can be expressed in the fewest possible bits per symbol, it is said to be encoded optimally. An optimal encoding of a stream of symbols uses H(S) bits.

To get more information about the source S one must deal with blocks of symbols rather than individual symbols. In a more general type of information source symbol  $s_i$  is dependent on one or more preceding symbols. This leads to a generalization of the zero-memory source and to the  $m^{th}$ -order Markov information source with a set of conditional probabilities.

For an  $m^{th}$ -order Markov source, the probability that a given symbol appears depends on the m preceding symbols. Considering the preceding m symbols,

$$(s_{i1},s_{i2},\ldots,s_{im})$$

as a single state then the conditional probability of the next symbol  $s_i$  is

$$P(s_i/s_{i1}, s_{i2}, \ldots, s_{im}).$$

The information obtained if  $s_i$  occurs while one is in state  $(s_{j1}, s_{j2}, \ldots, s_{jm})$  is

$$I(s_i/s_{i1}, s_{i2}, \dots, s_{im}) = -\log_2 P(s_i/s_{i1}, s_{i2}, \dots, s_{im}).$$

(2.3)

The average amount of information or entropy of the  $m^{th}$ -order Markov source S:

$$H(S) = -\sum_{S^{m+1}} P(s_{j1}, s_{j2}, \dots, s_{jm}, s_i) log_2 P(s_i/s_{j1}, s_{j2}, \dots, s_{jm})$$

(2.4)

where  $S^{m+1}$  is the  $(m+1)^{th}$  extension of the zero-memory source S. The probability of state  $(s_{j1}, s_{j2}, \ldots, s_{jm}, s_i)$  is  $P(s_{j1}, s_{j2}, \ldots, s_{jm}, s_i)$ :

$$P(s_{j1}, s_{j2}, \dots, s_{jm}, s_i) = P(s_i/s_{j1}, s_{j2}, \dots, s_{jm})P(s_{j1}, s_{j2}, \dots, s_{jm}).$$

(2.5)

A computer program is assumed to consist of a stream of symbols, the instructions. Measurements by Bennett [Bennett 1988] have already shown the dependency between opcodes and complete instructions. His entropy observations are shown in Table 2.3, giving the entropy for different order models.

| Entropy |              |                       |  |  |

|---------|--------------|-----------------------|--|--|

| Order   | Opcodes Only | Complete Instructions |  |  |

|         | bits/symbol  | bits/symbol           |  |  |

| 0       | 3.98         | 3.24                  |  |  |

| 1       | 2.87         | 2.64                  |  |  |

| 2       | 2.35         | 2.28                  |  |  |

| 3       | 2.03         | 2.01                  |  |  |

| 5       | 1.19         | 1.26                  |  |  |

| 10      | 0.13         | <del></del>           |  |  |

| 25      | 0.01         | <del></del>           |  |  |

Table 2.3: Entropy obtained by Bennett.

The reduction in entropy is nearly 28% from the zero order to the first order process. For fifth order he reaches one bit requirement per symbol and for higher order even less.

#### 2.6.2 Replacement of Repeated Strings

Wade and Stigall used information theory (and the concept of entropy) to attempt to estimate how much space object code should require [Wade & Stigall 1975]. Their approach was to treat instruction streams as a sequence of (independent) symbols. One of the simplest and most common ways to reduce the length of a symbol stream is to identify repeated strings and replace them with a single symbol [Wade & Stigall 1975]. If one assumes the string

$$s_1, s_2...s_k$$

occurs with probability  $P_s$  and is replaced by the new symbol s' whenever it occurs, then Wade and Stigall show the new value of entropy H' is given by

$$H' = -\frac{P_s}{1 - (k - 1)P_s} log_2(\frac{P_s}{1 - (k - 1)P_s})$$

(2.6)

$$-\sum_{i=1}^{k} \frac{P_i - P_s}{1 - (k-1)P_s} log_2(\frac{P_i - P_s}{1 - (k-1)P_s})$$

(2.7)

$$-\sum_{i=k+1}^{N} \frac{P_i}{1 - (k-1)P_s} log_2(\frac{P_i}{1 - (k-1)P_s})$$

(2.8)

The number of symbols to represent a string is reduced by factor

$$i-(k-1)P_s$$

The resulting change in entropy normalized to the length of the original string is given by

$$H_n - H = (1 - (k - 1)P_s)H' - H. (2.9)$$

where  $H_n$  is the normalized entropy. Wade and Stigall then considered the values of  $P_s$  for which the replacement results in a decrease of entropy. For small  $P_s$  they showed that this is given by

$$P_s > e \prod_{i=1}^k P_i$$

where e is the base of the natural logarithm. Their result quantifies the idea that a rarely occurring long string of symbols can often be replaced by a new symbol and save memory, while a shorter string must occur often to save memory.

The assumption made by Wade and Stigall that a stream of instructions can be considered as a sequence of independent symbols is very weak as shown by Bennett [Bennett 1988]. His opcode and instruction measurements show high dependency.

#### 2.6.3 Memory Referencing Behaviour

Hammerstrom and Davidson [Hammerstrom & Davidson 1977] used a similar analysis to estimate the information content of a memory referencing stream in the IBM S/360, using information theory. Specifically, they present techniques for analyzing computer addressing architectures and techniques for analyzing the efficiency of the addressing architecture and memory/CPU traffic of existing machines with regards to the information theory boundaries.

To obtain further improvement in memory/CPU bandwidth and CPU addressing efficiency, they suggest looking at higher order memories and accompanying radical changes in CPU architecture and compilation techniques. For the extension to higher order conditional probabilities they find a more useful definition of entropy.

Hammerstrom and Davidson also define the absolute entropy

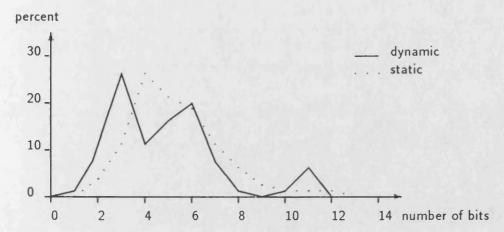

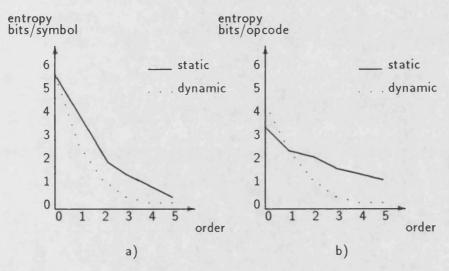

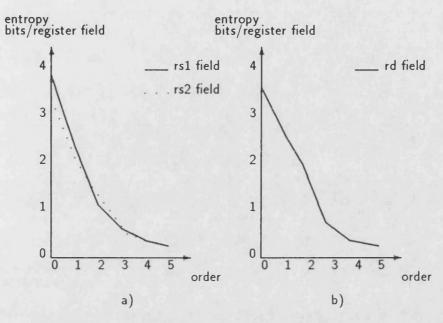

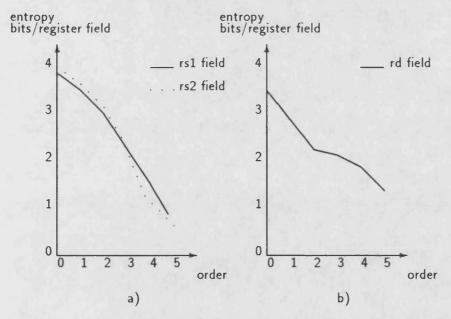

$$H_{\infty}(S) = \lim_{n \to \infty} H_n(S). \tag{2.10}$$